Ottobre 2021

Dispositivi con tecnologia 5G per una soluzione wireless O-RAN

a cura di: Brad Brannon, Systems Engineer, Analog Devices

Sommario

L’O-RAN è stata creata come catalizzatore nella trasformazione della comunità wireless, per abilitare nuovi canali di apparecchiature wireless e per accelerare l’innovazione al fine di mantenere le promesse fatte dal 3GPP sul 5G.1 Per avere successo ed essere economicamente efficiente, devono essere disponibili apparecchiature radio open source e dispositivi ottimizzati per la tecnologia 5G. Questo articolo esaminerà una di queste soluzioni per progettare e realizzare un sistema efficiente dal punto di vista energetico.

Quali sono le sfide del 5G?

Per raggiungere questi obiettivi esistono diverse tecniche utilizzate dai progettisti di reti e radio. Oltre a spostare i servizi dati agli estremi della rete, l’utilizzo di tecnologie massive MIMO e small cell aiuta ad aumentare sia la capacità che il throughput. La tecnologia Massive MIMO impiega numerose radio in un array per raggiungere non solo la capacità ma anche la copertura per una posizione centrale. Come il suo predecessore, la macrocella, una radio massive MIMO fornirebbe una copertura relativamente ampia intorno a questa posizione. Tuttavia, le radio massive MIMO sono impostate a frequenze più alte, in genere 2,6 GHz e oltre, che però non dispongono di una grande capacità di penetrazione negli edifici. Per arrivare a servire luoghi interni e altre aree esterne difficili da raggiungere, saranno utilizzate small cell. Con un significativo numero di luoghi interni ed esterni che vanno dalle abitazioni, alle installazioni aziendali fino alle aree commerciali e persino gli stadi, l’utilizzo delle small cell sarà cruciale per il successo del 5G. Dato il gran numero di small cell e la diversità delle implementazioni richieste in una rete, sarà indispensabile mantenere costi di installazione e gestione contenuti: questo sarà uno dei fattori chiave per il 5G.

Quali tecnologie sono disponibili?

Negli ultimi anni, diverse tecnologie si sono evolute verso una direzione che rende fattibili le soluzioni per il 5G. In primo luogo, dal punto di vista della base band, la legge di Moore continua non solo a ridurre il costo del silicio per gate, ma permette di integrare funzionalità più complesse nella tecnologia radio. Ora è possibile integrare molti degli algoritmi di controllo richiesti direttamente nella radio, comprese funzionalità come la predistorsione digitale (DPD – Digital Pre Distortion). Man mano che aumenta la disponibilità di nuove generazioni di radio aumenta il numero di possibilità.

In secondo luogo, alleanze come l’O-RAN2 stanno lavorando in tutto il settore wireless per abilitare economie di scala rivolte non solo alla riduzione dei costi, ma anche per migliorare la sicurezza della supply chain e offrire nuovi sistemi per far fruttare le reti wireless. In particolare, “l’O-RAN Alliance è stata fondata dagli operatori per definire con chiarezza i requisiti e aiutare a costruire un ecosistema di supply chain per realizzare i suoi obiettivi. Per raggiungere questi obiettivi, il lavoro della O-RAN Alliance incarnerà “i principi di apertura e intelligenza”.3 Come tale, le loro attività si concentrano sulla definizione delle interfacce fisiche specificate dal 3GPP in modo che possano essere standardizzate e implementate in tutto il settore come soluzioni interoperabili di tipo “white box”. Inoltre, O-RAN definisce anche i requisiti hardware e fornisce reference design per O-CU, O-DU e O-RU (Open Centralized Unit, Open Distributed Unit e Open Radio Unit, rispettivamente, come definito da O-RAN). Tutti insieme questi reference design permetteranno la standardizzazione dei processori fronthaul e baseband per ridurre ulteriormente il costo delle soluzioni. Insieme ad altri dispositivi 5G integrati come le radio integrate, i reference design possono servire a definire ciò che le small cell dovranno diventare, così come consentiranno l’implementazione degli standard. Il lavoro di queste alleanze rappresenterà un passaggio fondamentale.

In terzo luogo, la tecnologia radio si è rapidamente evoluta negli ultimi anni. Le radio ad alte prestazioni sono ora disponibili in diversi formati in grado di soddisfare gli standard di prestazione richiesti dal 3GPP nella specifica 38.104 e nei documenti correlati.1 Queste radio sono altamente integrate e includono non solo i componenti analogici e RF ma anche algoritmi critici come il DPD e riduzione del fattore di cresta (CFR – Crest Factor Reduction). Mentre queste radio sono costruite su CMOS fine-line, altre evoluzioni hanno avuto origine nei front-end RF dove i processi RF low cost (SiGe, SOI, GaN, GaAs, ecc.) stanno producendo LNA (Low-Noise Amplifier) altamente integrati e PA (Power Amplifier) ad alta potenza e alte prestazioni che possono vincere le sfide soddisfacendo le richieste imposte da questi standard.

Infine, sono disponibili soluzioni di alimentazione altamente integrate ed efficienti, tra cui Power over Ethernet (PoE), dispositivi di alimentazione standard, supervisione e monitoraggio e soluzioni di protezione, che possono fornire una power delivery compatta. Queste soluzioni offrono un’efficienza molto elevata e un rumore molto basso nell’ambiente radio e includono opzioni che proteggono dispositivi indispensabili come gli amplificatori di potenza.

L’insieme di queste tecnologie permette di realizzare piattaforme small cell a basso costo e ad alte prestazioni che possono essere efficacemente implementate dall’operatore in tutta la propria rete sia per sistemi a bassa che ad alta potenza.

Panoramica del sistema

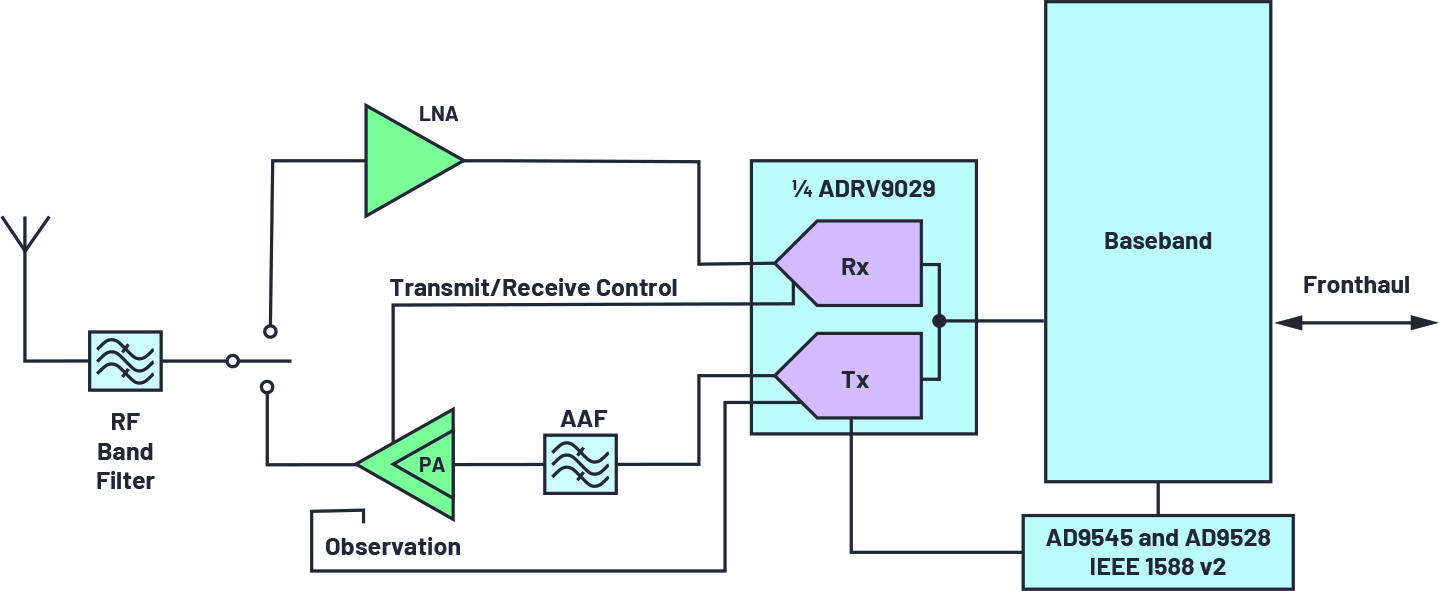

La Figura 1 mostra il tipico schema a blocchi di una small cell 5G 4T4R (quattro trasmettitori e quattro ricevitori). Ci sono molte combinazioni possibili, tra cui 2T2R e un range di classi di potenza da 24 dBm a salire. Questa figura farà da base per il resto dell’articolo, che si focalizzerà sui dispositivi con tecnologia 5G facilmente scalabili per le variazioni di banda e di livello di potenza all’interno dell’O-RU (Open Radio Unit).

Figura 1. Schema a blocchi di alto livello di una small cell.

Principali Elementi Radio

Nell’ultimo decennio, il transceiver integrato è maturato in una piattaforma ad alte prestazioni. La famiglia ADI RadioVerse™ comprende una vasta gamma di transceiver integrati che supportano fino a 200 MHz di larghezza di banda, integrando funzioni avanzate come il DPD. L’intera famiglia di questi prodotti non solo soddisfa le esigenze dei dispositivi con tecnologia 5G, ma continua anche a supportare i requisiti LTE e GSM RF multicarrier. Sebbene nuove generazioni di questi dispositivi siano in continuo sviluppo, una delle più recenti soluzioni è mostrata nella Figura 2, l’ADRV9029, una configurazione 4T4R. Sono disponibili altri prodotti che includono dispositivi con e senza DPD integrato e altre configurazioni, tra cui la 2T2R.

Ogni dispositivo RadioVerse comprende tutto il necessario per realizzare una radio completa, ad eccezione dell’LNA e del PA. Sono quindi incluse tutte le funzionalità per la trasmissione e la ricezione, i sintetizzatori e il clock, ed è compresa anche la macchina a stati e il VGA (Variable Gain Amplifier) necessario per eseguire l’AGC (Automatic Gain Control), il controllo del guadagno dell’amplificatore. Mentre i prodotti RadioVerse sono tutti a banda larga fino a 6 GHz, gli LNA e i PA non lo sono e devono essere specifici per banda o gamma di frequenza. Pertanto, per completare la progettazione della radio è necessario accoppiare un LNA e un PA adeguati all’IC RadioVerse. I prossimi paragrafi descriveranno la catena di segnale per la ricezione e la trasmissione per il progetto di una small cell 5G NR (New Radio) e forniranno alcune informazioni su come selezionare questi dispositivi.

Figura 2. Il transceiver ADRV9029

Esempio di Catena del Segnale del Ricevitore

Quando l’ADRV9029 è combinato con l’ADRF5545A, mostrato in Figura 3, può essere realizzato facilmente un ricevitore a 2 chip. È possibile utilizzare anche l’ADRF5515, essendo pin compatibile e, in combinazione con pochi altri componenti passivi, è possibile ottenere un design del ricevitore molto compatto e ad alte prestazioni, come mostrato nella catena del segnale in Figura 4. Il principale vantaggio di questa architettura è l’alto livello di integrazione, che porta non solo a un’implementazione a bassissimo costo ma anche alla minor dissipazione di potenza possibile.4

L’architettura della famiglia RadioVerse porta all’eliminazione di molti elementi tipicamente associati a un design classico del ricevitore, che comprende una parte dell’amplificazione RF, il filtraggio e l’integrazione di molte delle restanti funzionalità radio, compresi i filtri di canale (analogici e digitali) e gli amplificatori base band. Questi sono tipicamente fra i dispositivi più grandi e più potenti del sistema, la cui eliminazione si traduce in un risparmio significativo rispetto ad altre architetture come il campionamento RF diretto.

Figura 3. Il front-end del ricevitore TDD a doppio canale ADRF5545A

Come mostrato in Figura 4, la linea del ricevitore per small cell consiste in un circolatore RF (per applicazioni TDD – Time Division Duplex), l’ADRF5545A, un filtro SAW/BAW (surface acoustic wave/bulk acoustic wave) o filtro monoblocco, un balun e un transceiver. Non sono necessari amplificatori o VGA aggiuntivi, date le buone prestazioni di rumore e il basso IP1dB di ingresso dell’ADRV9029 e degli altri membri della famiglia RadioVerse. Utilizzando questa catena di segnale, è possibile soddisfare figure di rumore fino a 2 dB per il sistema completo, dall’antenna ai bit. Mentre questo design include un modulo front-end RF integrato (FEM), molti altri beneficeranno ancora di un design discreto ma non se ne discuterà in questo articolo. Il FEM integrato paga l’integrazione con un leggero aumento dei requisiti del filtro dell’antenna, ma offre comunque un design interessante per molte soluzioni altamente integrate come il massive MIMO e altre implementazioni TDD. Tipicamente, i front-end discreti sono usati per i progetti FDD (Frequency Division Duplex).

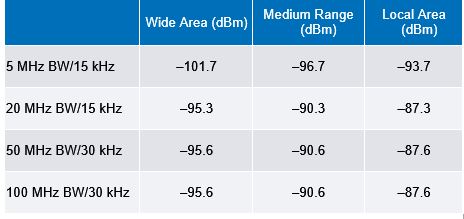

Ipotizzando una perdita prima dell’LNA di circa 0,5 dB, se la perdita del filtro di banda è di 1 dB, date le specifiche da datasheet dei due dispositivi attivi, la figura di rumore (NF – Noise Figure) nominale per la catena completa di segnale del ricevitore dovrebbe essere di circa 2 dB. Supponendo un rapporto segnale-rumore e distorsione di 0 dB coerente con l’MCS-4 (Modulation Coding Scheme), la sensibilità di riferimento sarà di circa -104.3 dBm per una portante G-FR1-A1-1 5G (~5 MHz). Questo risultato dovrebbe essere più che adeguato a soddisfare anche i requisiti di condotta per wide area mostrati nella sezione 7.2.2 della specifica 38.104 con spazio di tolleranza, e molto più che sufficiente per un progetto di area locale/small cell che richiede -93.7 dBm per questa condizione come riassunto nella tabella 1. Alcune applicazioni per small cell a basse prestazioni possono essere in grado di utilizzare un LNA a singolo stadio come il GRF2093 seguito da un filtro SAW.

Figura 4. Dettagli della catena di segnale del ricevitore.

Tabella 1. Classificazione dei ricevitori secondo la specifica 38.104

Inoltre, la specifica 38.104 nella sezione 7.4.1 richiede che al di sotto di -52 dBm (wide area) di blocco ACS, il ricevitore non superi i 6 dB di desense. In base al NF rispetto al livello d’ingresso mostrato in Figura 5, a -52 dBm si ha meno rumore aggiuntivo rispetto ai livelli inferiori. Infatti, il rumore di fondo non subisce incrementi verso l’alto se non poco dopo i -40 dBm, caratteristica ideale per l’ACS locale che richiede una tolleranza di -44 dBm.

I requisiti generali di blocco (7.4.2) richiedono un aggressore di -35 dBm (local area) da applicare al ricevitore all’interno della banda interessata ad un offset di ±7.5 MHz con non più di 6 dB di desense consentito. Stando alla Figura 5 che mostra le prestazioni della catena di segnale Analog Devices, si può notare che si verifica solo uno 0,9 dB circa di desense. Il blocco della banda stretta rappresenta un impulso di potenza leggermente inferiore simile al CW (Continuous Wave), ma non è un problema.

Figura 5. NF vs. livello di ingresso del Ricevitore.

Probabilmente una sfida più interessante sarà il blocco fuori banda della sezione 7.5.2. In questo caso un segnale di -15 dBm viene fatto passare all’ingresso dell’antenna. Per una small cell con meno di 200 MHz, il livello più vicino dove questo segnale può trovarsi al margine della banda è 20 MHz. Il test richiede uno sweep da 1 MHz fino a 12,75 GHz, escludendo la banda entro 20 MHz dalla frequenza operativa. Ci sono diversi fattori che in questo caso lavorano a vantaggio della catena di segnale. Innanzitutto, il circolatore ha una larghezza di banda limitata e respingerà molti segnali fuori banda, ma a ragion veduta non rappresenta grande contributo. In secondo luogo, il filtro mostrato dopo l’ADRF5545A fornirà un po’ di filtraggio; tipicamente 20 MHz fuori banda ~ 20 dB di reiezione sono livelli ragionevoli. Infine, una delle caratteristiche uniche e più utili della famiglia di transceiver ADI, inerente all’architettura del transceiver, è la reiezione fuori banda integrata. Nella Figura 20 della nota applicativa AN-1354 di Analog Devices, la reiezione intrinseca fuori banda è dimostrata come un livello di segnale crescente per il desensing del ricevitore. In questa nota applicativa, la frequenza di sweeping in entrambe le direzioni attorno alla banda passante mostra che un segnale più grande è tollerato per lo stesso livello di desensing. Nella nota applicativa, vediamo che vicino al limite della banda sono possibili circa 10 dB per 6 dB di desensing. Al di là di queste considerazioni, il filtro integrato elimina in modo significativo i segnali fuori banda, che non hanno alias e sono ampiamente mitigati sia dal filtro on-chip che da quello esterno.

Nel complesso questi blocchi filtrano l’aggressore fuori banda di -15 dBm a partire da circa -40 dBm fino a -45 dBm e fino alla banda di esclusione di 20 MHz. Andando oltre questi valori, è logico aspettarsi una reiezione ancora maggiore. A questo livello, la Figura 5 mostra quanto poco desense ci si può aspettare.

Forse il problema più grande sarebbe la linearità del modulo front-end. A questo livello si potrebbe prevedere un significativo prodotto di intermodulazione IM3. A seconda del FEM selezionato, potrebbe essere opportuno spostare il filtro di selezione della banda prima del secondo LNA per proteggerlo dai segnali fuori banda, segnali che tipicamente producono IM di grandi dimensioni. Non è possibile posizionare un filtro fra stadi su questo tipo di FEM, quindi deve essere implementata un’opzione alternativa.

Per aiutare a limitare l’impatto dell’intermodulazione derivata da grandi blocchi fuori banda, un tipico FEM include switch di bypass del secondo stadio per ridurre il guadagno e proteggere il secondo stadio dalla non linearità, come mostrato nella Figura 3. Alterare il guadagno dell’LNA riduce l’SNR (Signal Noise Ratio) della catena di segnale di 1 dB, ma aiuta a preservare la gamma dinamica complessiva limitando la distorsione di intermodulazione causata dai grandi segnali bloccanti, in maggior misura rispetto alla compensazione della perdita di prestazioni di rumore. Nel complesso, in un NF questo valore risulterebbe di circa 5,7 dB nel peggiore dei casi, livello che ad ogni modo rientra ancora all’interno del requisito di footprint local area (small cell) sulla sensibilità di riferimento. Qualsiasi requisito rimanente riferito al filtraggio è soddisfatto da un filtro d’antenna, e la reiezione può essere determinata in base al punto di compressione a basso guadagno e di IP3 del ricevitore FEM.

Esempio di Catena di Segnale del Trasmettitore

Quando l’ADRV9029 è combinato con un amplificatore RF specifico, o RFVGA (visitare analog.com/rf per ulteriori opzioni), e un PA adatti, si può facilmente realizzare una picocella interna compatta, una picocella esterna o una microcella esterna5. Con solo pochi altri componenti passivi, questi dispositivi con tecnologia 5G possono essere combinati per dare forma a un design del trasmettitore molto compatto ed efficiente, come mostrato nella catena di segnale in Figura 6. Il principale vantaggio di questa architettura è il più alto livello di integrazione possibile, che porta non solo a un’implementazione a costo ridotto ma anche alla più bassa dissipazione di potenza possibile sfruttando la funzionalità DPD integrata disponibile su alcuni transceiver ADI.

Come mostrato nella Figura 6, la linea del trasmettitore per small cell consiste in un circolatore, un PA, un filtro e un transceiver. Inoltre, il circuito include un accoppiatore sull’uscita del PA che viene utilizzato per monitorare la distorsione di uscita (e può anche essere impiegato per monitorare il VSWR, Voltage Standing Wave Ratio, dell’antenna così come la potenza diretta) e può essere utilizzato con il DPD per migliorare l’efficienza operativa della funzione di trasmissione e migliorare le prestazioni sulle spurie. Sebbene sia possibile utilizzare un DPD esterno, alcuni transceiver ADI includono DPD completamente integrati, che operano con 350 mW o meno di potenza incrementale a seconda della quantità di correzione richiesta da un determinato PA. I PA di potenza inferiore richiederanno meno correzione e quindi meno potenza richiesta dal DPD. Inoltre, il DPD integrato riduce della metà il numero di corsie SERDES (Serializer/Deserializer) verso il chip esterno in banda base, poiché le corsie SERDES del ricevitore di osservazione vengono eliminate completamente e il carico utile del trasmettitore è ridotto, dato che l’espansione della larghezza di banda per il DPD è gestita completamente all’interno del transceiver. Un DPD equivalente in un FPGA (Field Programmable Gate Array) ha tipicamente una potenza 10 volte più alta e non è efficiente o efficacie dal punto di vista energetico per small cell low power e massive MIMO. Tuttavia, integrando il DPD nel transceiver, la potenza molto bassa e il costo contenuto permettono effettivamente di utilizzare il DPD anche per le small cell low power e quindi di trarre vantaggio dall’efficienza e dalla migliore linearità di trasmissione senza un pesante carico di calcolo esterno.

La Figura 7 e la Figura 8 mostrano esempi di funzionamento del DPD di ADI in applicazioni per small cell a bassa e media potenza. L’impulso mostrato è riferito a cinque portanti LTE adiacenti da 20 MHz per un totale di 100 MHz. Tipicamente nella maggior parte delle implementazioni, l’LTE richiede un minimo di 45 dB ACLR (Adjacent Channel Leakage Ratio) nella previsione di ottenere di più di questo valore. ADI esamina sempre nuovi PA di tutte le classi di potenza attraverso un laboratorio di test continuativi. Controlla il Power Amplifier Test Report, o consulta ADI per gli ultimi dettagli sulla tecnologia DPD disponibile come anche l’elenco degli ultimi PA qualificati.

Figura 6. Dettagli della catena di segnale del trasmettitore.

Figura 7. Spettro tipico del PA con e senza DPD RF totale di 26 dBm.

Figura 8. Spettro tipico del PA con e senza DPD RF totale di 37 dBm.

Come si Mette Tutto Insieme?

La Figura 9 mostra l’intera catena di segnale, compresi alcuni dei segnali di controllo richiesti. Per l’efficienza energetica, il circuito include la segnalazione di trasmissione e ricezione per abilitare e disabilitare gli amplificatori durante i loro rispettivi cicli di TDD. Allo stesso modo, questa configurazione potrebbe essere usata con l’FDD per lo spegnimento durante gli slot inutilizzati riuscendo anche in questo caso a risparmiare energia. Uno switch è anche necessario per modificare l’ingresso dell’LNA, in modo da deviare qualsiasi potenza di trasmissione di ritorno a una terminazione invece che all’ingresso dell’amplificatore. Tutti questi segnali possono essere generati e orchestrati dall’ASIC, dall’FPGA o dal transceiver.

La catena del segnale del ricevitore include una funzione che modifica il flusso dati digitale per tenere conto del guadagno analogico ridotto, preservando il livello del segnale assoluto mentre viene inviato al low-PHY e poi a valle al resto della base band.

L’applicazione mostrata è riferita alla banda singola. Mentre il transceiver è a banda larga e copre tutte le frequenze fino a 6 GHz, non tutti i dispositivi nel progetto sono in grado di farlo. Dispositivi come l’LNA e il PA lavorano tipicamente in banda e richiedono una selezione basata sulla banda supportata. In genere, sono disponibili in opzioni pin-compatibili per coprire tutte le bande comuni al di sotto dei 6 GHz e sono di facile sostituzione. Queste caratteristiche permettono di supportare le bande TDD e FDD più diffuse, comprese quelle per il 5G e quelle proposte per l’O-RAN.

Clock Tree

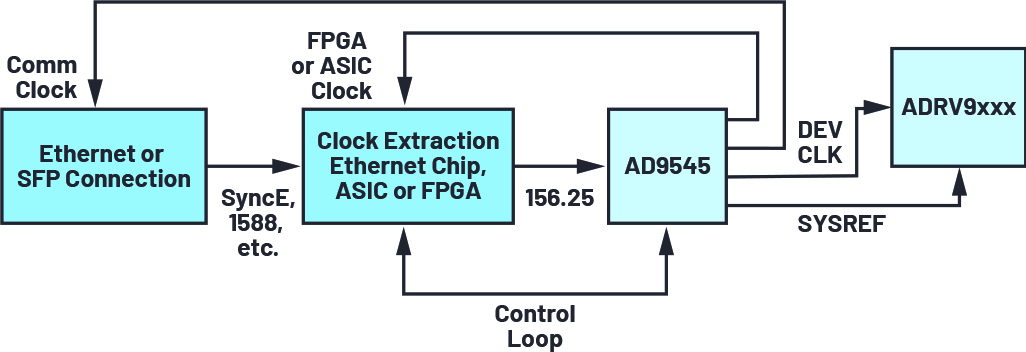

A seconda della configurazione, sono possibili diverse configurazioni di clock. Se è richiesto un preciso allineamento temporale, allora sarà necessaria una sintesi del clock a 2 stadi. Il primo stadio richiederà il collegamento alla base band per mezzo di un ASIC, FPGA o controller per temporizzare e allineare correttamente la digitalizzazione radio. Questa applicazione richiederà l’elaborazione delle informazioni del protocollo PTP (Precision Time Protocol) fornite attraverso il fronthaul o da un ricevitore GPS locale. Questo assicurerà che radio e processore base band siano in grado di sapere esattamente quando i frame radio dovranno essere elaborati.

La famiglia AD9545 è ideale per regolare con precisione la frequenza, la fase e il tempo di clock principale della radio. Ha il vantaggio che può essere configurato per funzionare temporaneamente senza un riferimento e mantenere la precisione nel caso di un clock di riferimento difettoso o intermittente quando è accoppiato con un TCXO (temperature compensated crystal oscillator) o OCXO (oven controlled crystal oscillator).

Per le configurazioni che non richiedono l’allineamento temporale di precisione o come secondo stadio di quelle che lo richiedono, è necessario un dispositivo di distribuzione del clock. Lo scopo del dispositivo di distribuzione è generare la gamma di clock in tutta la radio. Ciò include quelli richiesti per JESD, eCPRI, Ethernet, SFP e i principali segnali in tutta la radio. L’AD9528 fornisce clock a basso jitter, in totale fino a 14 velocità diverse, compreso il supporto per il clock device (convertitori JESD204B/JESD204C) e la segnalazione SYSREF (system reference).

Uno schema a blocchi di clock a 2 stadi è mostrato in Figura 10. Per applicazioni che non richiedono un preciso allineamento temporale, l’AD9545 può essere eliminato o bypassato e verrà utilizzato solo l’AD9528. Il clock in ingresso al sistema proviene dalla temporizzazione di base della rete e viene recuperato dalla banda base e dalla funzionalità di rete del blocco funzione Ethernet o all’interno dell’FPGA, a seconda dell’architettura. Sono possibili svariate configurazioni alternative a seconda dei requisiti specifici della radio, di cui solo una rappresentazione è mostrata qui.

Figura 9. Catena di segnale completa del transceiver.

Figura 10. Esempio di clock tree

Potenza

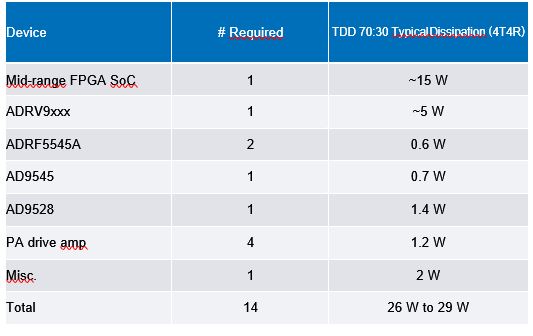

La dissipazione di potenza totale è determinato da molti fattori. Tra questi fattori ci sono l’FPGA selezionato e le funzioni implementate, il transceiver selezionato e le opzioni abilitate, il clock tree richiesto e la potenza RF generata.

Un tipico SoC FPGA di fascia media che implementa l’elaborazione O-RAN CUS- e M-plane, insieme alla sincronizzazione con lo stack PTP IEEE 1588 v2, consumerà circa 15 W. Il tipico transceiver ADRV9029 dissiperà tra 5 W e 8 W, a seconda della configurazione TDD o FDD insieme alla gamma di funzionalità DFE abilitate. A questo deve essere aggiunta la potenza del clock, quella del ricevitore e del trasmettitore, così come le varie potenze in gioco. La tabella 2 mostra un esempio di rollup della potenza totale per il sistema al netto della catena del trasmettitore, che varia notevolmente con la classe di potenza in uscita.

Aumentando la dissipazione di potenza per la radio, la dissipazione totale per un duty cycle 70:30 per Tx:Rx mostra da 26 W a 29 W, a seconda della configurazione precisa della radio escludendo la potenza associata al PA. La tabella 3 mostra alcuni esempi di dissipazione del PA. Poiché i PA operano in gran parte nella zona lineare dei transistor in qualche variazione della classe AB, la loro efficienza potrebbe risultare in un qualsiasi punto compreso tra il 20% e il 50%. Ed è qui che il valore del DPD integrato è un grande vantaggio. Anche per i PA di piccola larghezza di banda e low power, qualche decina di mW di dissipazione DPD è più che compensata dal miglioramento dell’efficienza del PA.

Tabella 2. Stima della Dissipazione della Potenza

Tabella 3. Dissipazione della Potenza di Trasmissione

Per una small cell a bassa potenza, l’aggiunta di circa 2,5 W di potenza porta la dissipazione totale a circa 30 W, che va benissimo per una small cell interna raffreddata passivamente e alimentata da una soluzione PoE.

Una potenziale soluzione PoE è illustrata nella Figura 11. Questa soluzione include un bridge controller LT4321 che permette di usare i transistor MOS come diodi invece dei raddrizzatori, il cui vantaggio è l’efficienza notevolmente migliorata. Il bridge controller è seguito dall’LT4295, un dispositivo PD conforme a 802.3bt. Questo può essere seguito da appropriati regolatori locali al fine di soddisfare i requisiti mostrati nella tabella precedente, fornendo fino a 90+ W come richiesto.

Figura 11. Soluzione di alimentazione isolata PoE per small cell.

Oltre ai dispositivi di conversione PoE, sono disponibili molti altri dispositivi a supporto del reference design per small cell. Questi ultimi includono dispositivi fondamentali come la famiglia ADP5054, che è specificamente progettata per alimentare i transceiver ADI così come molti altri convertitori buck e regolatori LDO a basso rumore, come mostrato nella Figura 12.

Opzioni

Una delle grandi qualità di questa architettura radio è la flessibilità che permette di soddisfare una serie di requisiti di mercato. Questa architettura è ottimizzata per una gamma di applicazioni che includono sia FDD che TDD ed è sempre in grado di garantire prestazioni in banda bassa, media e alta ed è adatta alle small cell attraverso piattaforme massive MIMO. Possono essere effettuati diversi compromessi sia nei circuiti del trasmettitore che del ricevitore ottimizzando così costi, dimensioni, peso e potenza. Sebbene questo articolo si concentri su integrazione e prestazioni più elevate, è possibile fare alcuni semplici compromessi a favore del costo con selezioni leggermente diverse.

Ad esempio, alcuni PA low power non richiedono un amplificatore drive e quindi potrebbero non essere necessari. Poiché la potenza RF è bassa per molte applicazioni su small cell, il circolatore può essere sostituito da un semplice switch TR. Infine, se sono richieste solo prestazioni locali, l’LNA a doppio stadio può essere sostituito da un semplice LNA a stadio singolo. Il risultato è un’opzione low cost in grado di fornire prestazioni radio ancora buone. Un esempio di ciò è mostrato nella Figura 13. Molte altre configurazioni sono disponibili per ottenere un’ampia gamma di possibilità attraverso un vasto range di opzioni di frequenza e potenza.

Figura 12. Un tipico power tree per applicazioni small cell.

Figura 13. Catena di segnale del transceiver alternativo.

Figura 14. Piattaforma-prototipo 5G con front-end RF re-bandable.

Conclusioni

I dispositivi con tecnologia 5G qui descritti sono disponibili per applicazioni di comunicazione e consentono implementazioni low cost adatte allo sviluppo del 5G, specialmente quelle che riguardano soluzioni O-RAN O-RU. Queste includono dispositivi della famiglia RadioVerse, così come amplificatori RF, ripristino/sincronizzazione del clock e Power over Ethernet/regolazione del punto di carico. Insieme, questo set di dispositivi altamente integrati è pronto per l’implementazione di applicazioni 5G small cell, macrocell, microcell e massive MIMO.

In combinazione con PHY e software adeguati in un FPGA, eASIC, o ASIC, è possibile sviluppare una soluzione O-RU completa. La Figura 14 mostra l’esempio di una piattaforma sviluppata con i partner di Intel®, Comcores e Whizz Systems. Queste soluzioni soddisfano non solo le caratteristiche RF necessarie, ma anche i budget di costo e di potenza richiesti per consentire l’implementazione di piattaforme O-RAN low cost ad alte prestazioni.

——————————————————–

Riferimenti

1 ftp://ftp.3gpp.org/specs/latest/Rel-15/38_series/

3 “O-RAN: Towards an Open and Smart RAN.” O-RAN Alliance, October 2018.

4 Brad Brannon. “Where Zero-IF Wins: 50% Smaller PCB Footprint at 1/3 the Cost.” Analog Dialogue, Vol. 50, No. 3, September 2016.

5 Specifications. O-RAN Alliance.